# THERMAL MANAGEMENT AND ELECTROMECHANICAL NOISE SUPPRESSION IN A PORTABLE JOSEPHSON JUNCTION VOLTAGE STANDARD

by

# Namit Singh

A dissertation submitted to the faculty of The University of North Carolina at Charlotte in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Mechanical Engineering

Charlotte

2012

| Approved by:          |

|-----------------------|

| Dr. James F. Cuttino  |

| Dr. Deborah L. Sharer |

| Dr. Stuart T. Smith   |

| Dr. Faramarz Farahi   |

© 2012 Namit Singh ALL RIGHTS RESERVED

#### **ABSTRACT**

NAMIT SINGH. Thermal management and electromechanical noise suppression in a portable Josephson junction voltage standard. (Under the direction of DR. JAMES F. CUTTINO)

A self-contained, fully portable, Josephson junction voltage reference standard system has been designed, developed and tested. The system relies on an active, closed-cycle refrigerator (CCR) cryocooler system and completely eliminates the reliance on liquid helium for cooling the Josephson Junction Array (JJA) chip to the required superconducting temperature of approximately to 4.2 K. The CCR based system has performance capabilities comparable to the liquid helium Dewar-based system and is packaged to operate as a portable system in environments like the US Army's calibration vans or calibration labs that do not have access to liquid helium.

The use of a CCR based cryocooling system brings forth many challenges not found in the classic Dewar-based system. This work identifies the principal challenges for achieving an operating system, and provides unique solutions to overcoming two areas of significant concern, thermal management and electromagnetic noise.

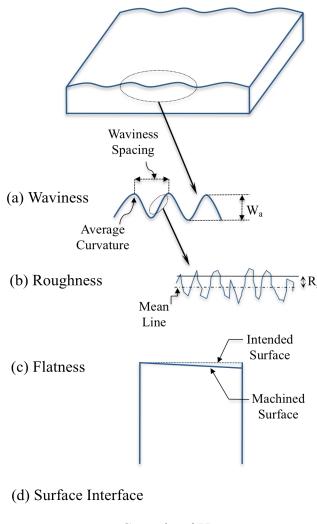

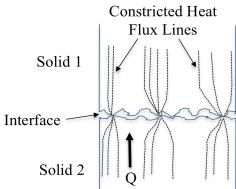

Dewar based systems provide three-dimensional convective cooling. While very effective in cooling, they are inappropriate for portable labs and are subject to evaporation. The challenge for an active system is in providing adequate thermal management to ensure sufficient cooling despite having only one-dimensional conductive cooling. An extensive study was conducted into various methodologies for mounting the chip in the new system and ensuring that superconducting temperatures were obtained. The surface roughness of a conventional machined surface is in the range of several

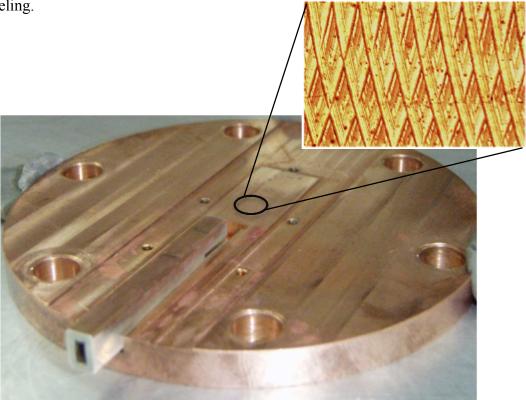

micrometers. The random peaks and valleys of the surface offer insufficient contact area between the cryocooler cold-head and the Josephson junction array chip, resulting in higher than superconducting temperatures at the JJA chip surface. Several approaches researched to increase the thermal contact conductance included thermal grease, adhesives and other high conductivity interstitial materials. The solution provided in this research is an elegantly simple technique, which eliminated the introduction of viscous materials or adhesives, thereby improving the maintainability of the chip. An innovative chip-mount was designed and machined using a state-of-the-art diamond turning technique to achieve a surface roughness of lower than 5 nm and completely eliminate the use of any foreign material. The diamond turned surface attained an operational temperature of  $4.2 \pm 0.2$  K indicating a 30% improvement in the ability to cool the JJA chip.

The second area of interest is understanding the presence of magnetic fields and electromagnetic noise in the vicinity of the JJA chip and eliminating or greatly reducing them. High permeability MuMetal® magnetic shields were designed and installed to reduce the presence of magnetic field by up to 90%, and the nature of magnetic field noises were experimentally quantified. Performance deterioration due to the presence of electromagnetic noise induced by the cryocooler, motor and pump was expected, but for the first time detailed experiments were conducted to measure the magnetic fields in the system, understand their effects, and systematically eliminate or reduce them.

The final system was assembled and the performance was verified using standard Josephson voltage standard (JVS) system practices. A comparison of different operational parameters for the CCR based system was done with the laboratory based

liquid helium cooling system, and the results were found to be comparable. The values for critical current and the step amplitude for the JJA chip (# 2629B11) were reported by the chip manufacturer to be 110  $\mu$ A and 29  $\mu$ A, respectively, tested with a liquid helium system; the same values were measured to be 112  $\mu$ A and 27  $\mu$ A, respectively, while operating in the UNC-Charlotte JVS system. The measured values were within the experimental repeatability of 5% and the nature of characteristic I-V curves and voltage steps were similar to the measurements made in the liquid helium system. These comparisons demonstrated the operational capabilities of the UNC-Charlotte CCR based Josephson voltage standard system.

#### **ACKNOWLEDGEMENTS**

I would like to express my deepest gratitude to Dr. James Cuttino for his continuous guidance, encouragement and support throughout this research. I want to thank him for taking the proactive role of a true mentor that has positively influenced my career and has helped me in developing my professional acumen in ways that cannot be expressed in words. I am truly indebted to him for all the motivation he has provided by always being there to help and for sharing his time and wisdom. Special thanks goes out to Dr. Stuart Smith who has been an inspiration and a person that I have always looked up to as a teacher, a guide and a researcher. Knowingly and unknowingly he has guided me a lot and I want to thank him from the bottom of my heart. I also want to thank Dr. Deborah Sharer for all the guidance and direction that she has provided all through this research project. I would like to thank Dr. Faramarz Farahi for taking out time and being a member of the research committee. Also, I am thankful to Dr. Matt Davies and Mr. Brian Dutterer for helping us with the Diamond Turning Machine operation and to Dr. Jimmie Miller for all his help with the AFM machine and for all the helpful discussions.

I would like to thank United States Army Primary Standards Laboratory (APSL) for providing the funding and technical assistance for this project. I am grateful to Dr. Clark Hamilton of VMetrix LLC for sharing his vast knowledge and expertise in the field of Josephson Voltage Standards and to Dr. Elie Track and Dr. Masoud Radparvar, from Hypres, Inc., for the critical technical guidance.

On a personal front, I would like to thank my parents and my brother for all the love and encouragement they have provided throughout my life, without which none of this would have been possible. I would like to thank my wife, Molishree, for her patience and love through this arduous journey; you bring true joy and meaning to my life. Also, I would like to thank my graduate colleagues Maruti and Gaurav for all the help and numerous technical discussion sessions and special thanks to my closest friends Hemal, Premal, Soumajit and Doyel for their special friendship and for always being there.

# TABLE OF CONTENTS

| LIST OF F | IGURES                                    | xi   |

|-----------|-------------------------------------------|------|

| LIST OF T | ABLES                                     | xiii |

| LIST OF A | ABBREVIATIONS                             | xiv  |

| CHAPTER   | 1: INTRODUCTION                           | 1    |

| 1.1       | Research Motivation                       | 2    |

| 1.2       | Structure of Dissertation                 | 7    |

| CHAPTER   | 2: VOLTAGE STANDARD                       | 9    |

| 2.1       | Introduction                              | 9    |

| 2.2       | Principles of Superconductivity           | 10   |

| 2.3       | Josephson Junction Voltage Standard       | 16   |

| 2.4       | Dewar-based Voltage Standard System       | 21   |

| 2.5       | Design of a Portable System               | 22   |

|           | 2.5.1 Thermal and Cryogenic System        | 23   |

|           | 2.5.2 Magnetic Shielding                  | 25   |

|           | 2.5.3 Microwave Source                    | 25   |

|           | 2.5.4 Layout of the Portable System       | 28   |

| CHAPTER   | 3: THERMAL MANAGEMENT                     | 31   |

| 3.1       | Cryocooling system                        | 31   |

| 3.2       | Vacuum System                             | 34   |

| 3.3       | Mounting of Josephson Junction Array Chip | 38   |

| 3.4       | Thermal Radiation Shield                  | 41   |

| 3.5       | Conclusion                                | 45   |

|                                                                     | ix  |

|---------------------------------------------------------------------|-----|

| CHAPTER 4: THERMAL CONTACT CONDUCTANCE                              | 48  |

| 4.1 Introduction                                                    | 48  |

| 4.2 Thermal Contact Conductance                                     | 50  |

| 4.3 Mathematical Model and Problem Definition                       | 53  |

| 4.4 Conceptual Design and Approach                                  | 57  |

| 4.4.1 Application of Pressure                                       | 57  |

| 4.4.2 Use of Interstitial materials                                 | 61  |

| 4.4.2.1 Apiezon® N Grease                                           | 62  |

| 4.4.2.2 Indium Foil                                                 | 63  |

| 4.4.3 Mounting- Diamond Turned Machining                            | 66  |

| CHAPTER 5: MAGNETIC FIELD CHARACTERIZATION                          | 82  |

| 5.1 Magnetic Field and Superconductors                              | 83  |

| 5.2 Critical Magnetic Field                                         | 84  |

| 5.3 Magnetic Shielding                                              | 85  |

| CHAPTER 6: RESULTS                                                  | 96  |

| 6.1 Performance characteristics for the cryocooler based JVS system | 96  |

| 6.1.1 Temperature performance                                       | 96  |

| 6.1.2 Magnetic Shielding performance                                | 98  |

| 6.1.3 Electromagnetic Noise                                         | 101 |

| 6.2 Josephson Voltage Standard Operational Tests                    | 102 |

| 6.2.1 Frequency Uncertainty and Correction                          | 102 |

| 6.2.2 Self Test with $10 \text{ k}\Omega$ test box                  | 103 |

| 6.2.3 I-V Curve for the JJA Chip                                    | 104 |

| 6.2.4 Voltage Steps                                                 | 108 |

| 100 | X   |

|-----|-----|

|     | 109 |

| CHAPTER 7: CONCLUSIONS | 109 |

|------------------------|-----|

| REFERENCES             | 112 |

# LIST OF FIGURES

| FIGURE 1.1: | Diagrammatic representation of a Weston cell                                                                                                                                                                                                        | 3  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| FIGURE 1.2: | Approximate level of agreement in dc voltage measurements among National Measurement Institutes (NMI's) from 1930-2000                                                                                                                              | 5  |

| FIGURE 2.1: | Lattice distortion and electron Cooper pairs in superconductors                                                                                                                                                                                     | 13 |

| FIGURE 2.2: | I-V characteristic of a single Josephson junction with 96 GHz microwave power applied                                                                                                                                                               | 18 |

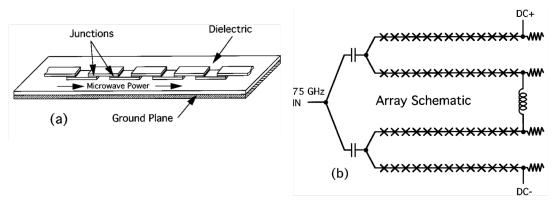

| FIGURE 2.3: | Diagrammatic representation of Josephson junction array and the circuit                                                                                                                                                                             | 20 |

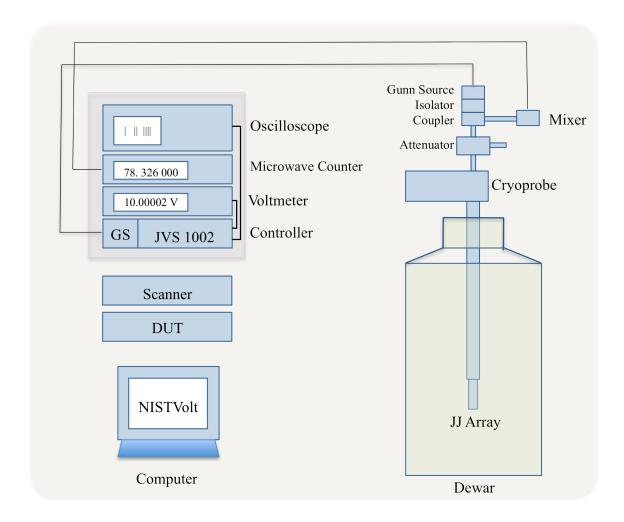

| FIGURE 2.4: | Liquid helium Dewar based Josephson voltage standard system                                                                                                                                                                                         | 22 |

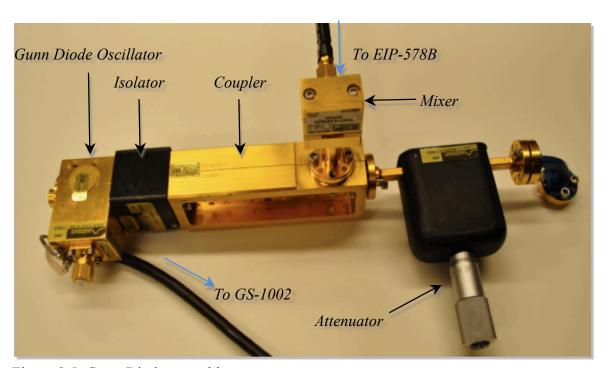

| FIGURE 2.5: | Gunn diode assembly                                                                                                                                                                                                                                 | 27 |

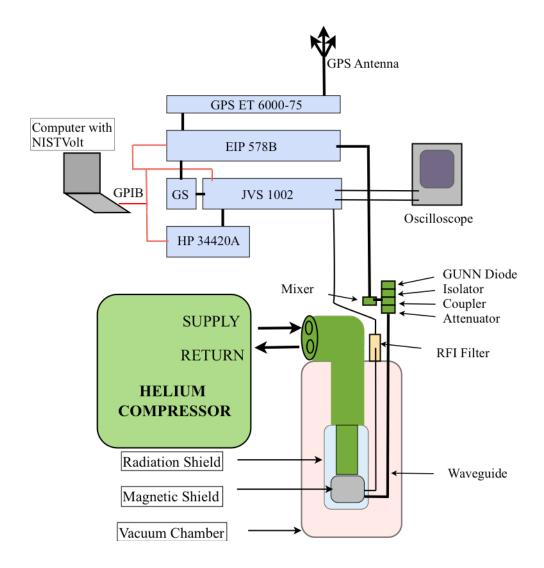

| FIGURE 2.6: | Diagrammatic representation of the assembled portable Josephson voltage standard system                                                                                                                                                             | 29 |

| FIGURE 3.1: | Closed circuit refrigerator based cryocooling system                                                                                                                                                                                                | 32 |

| FIGURE 3.2: | Diagrammatic representation of the cryocooling and vacuum system                                                                                                                                                                                    | 35 |

| FIGURE 3.3: | Redesigned compressor unit, cryocooler assembly and the vacuum system mounted on a standard rack mount                                                                                                                                              | 37 |

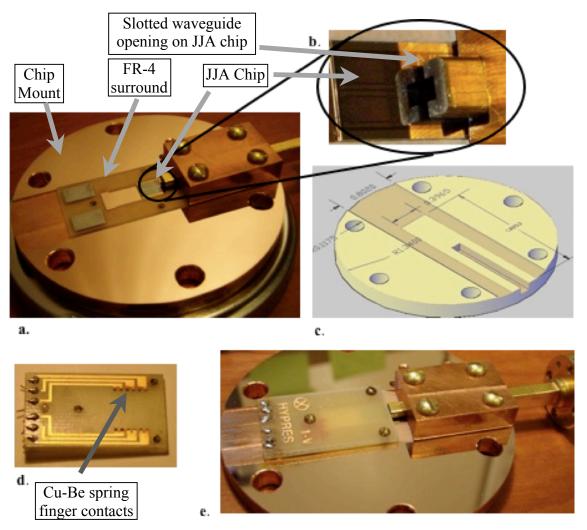

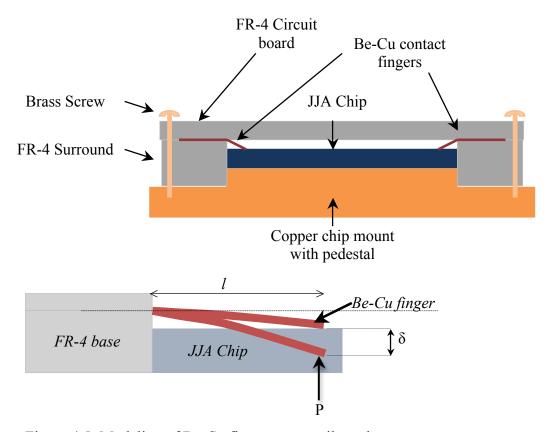

| FIGURE 3.4: | (a) Image of chip mount with the JJA chip and FR-4 surround (b) position of waveguide and JJA chip, (c) dimensional representation of chip mount, (d) FR-4 circuit board with Cu-Be spring finger contacts, and (e) complete assembly on chip mount | 39 |

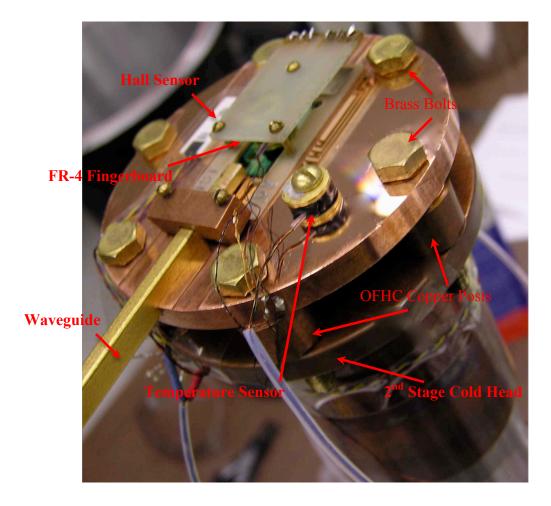

| FIGURE 3.5: | Image of the chip mount assembly attached to the 2 <sup>nd</sup> stage coldhead of the cryocooler                                                                                                                                                   | 40 |

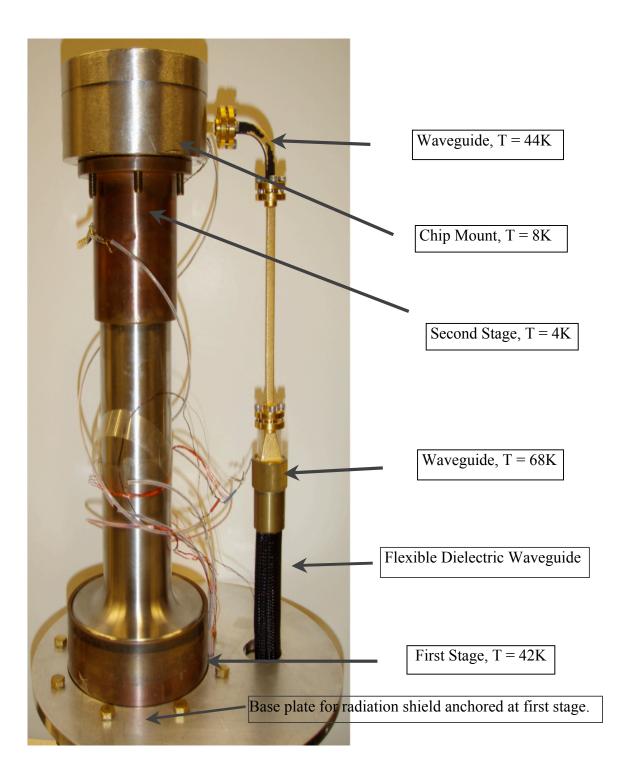

| FIGURE 3.6: | Temperature distribution on the waveguide                                                                                                                                                                                                           | 44 |

| FIGURE 4.1: | Surface characteristics of contacting surfaces                                                                                                                                                                                                      | 51 |

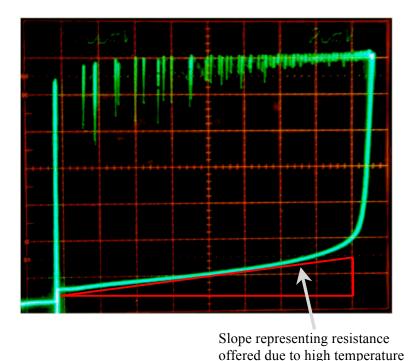

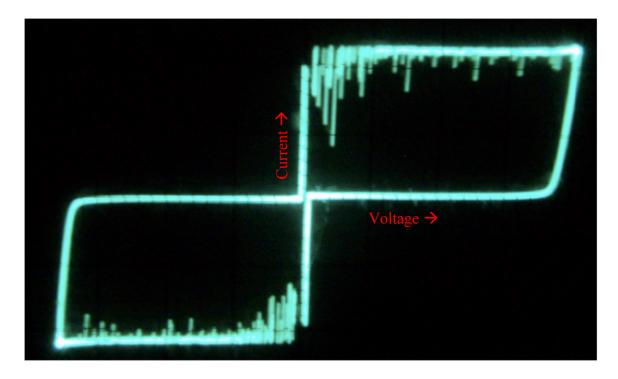

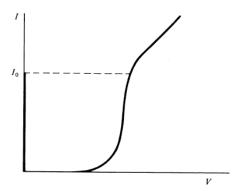

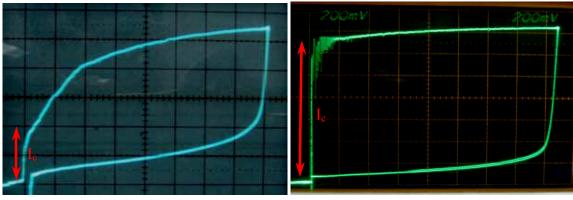

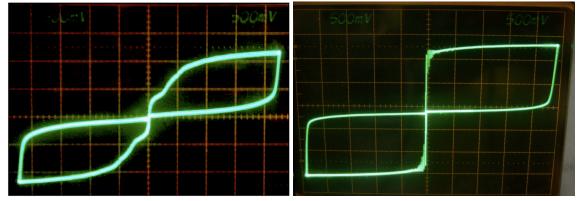

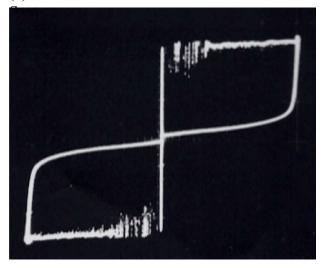

| FIGURE 4.2: | I-V curve displaying current loss due to high temperature                                                                                                                                                                                           | 54 |

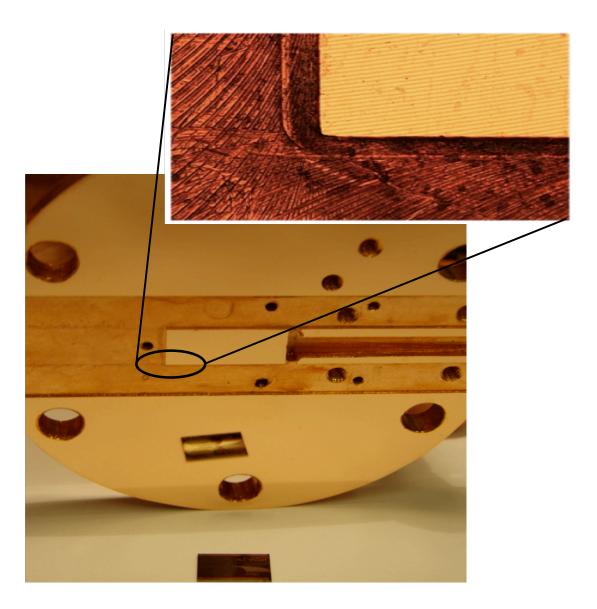

| FIGURE 4.3: | Optical microscope image of the chip mount showing the machining tool marks                                                                                                                                                                         | 55 |

|                                                                                                                                 | xii |

|---------------------------------------------------------------------------------------------------------------------------------|-----|

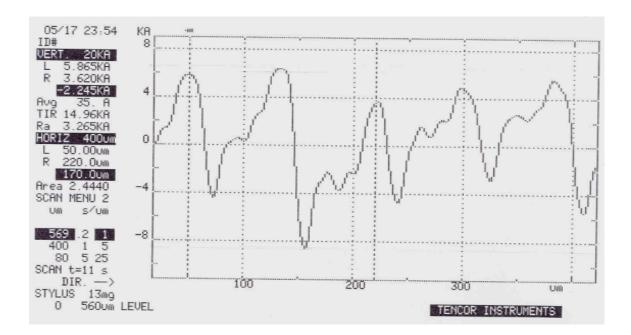

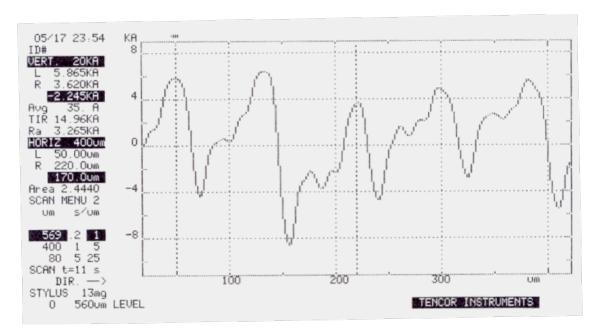

| FIGURE 4.4: Surface profilometer plot of a conventional machined surface                                                        | 56  |

| FIGURE 4.5: Modeling of Be-Cu finger as a cantilever beam                                                                       | 59  |

| FIGURE 4.6: I-V curve obtained for the 10-V JJA chip                                                                            | 65  |

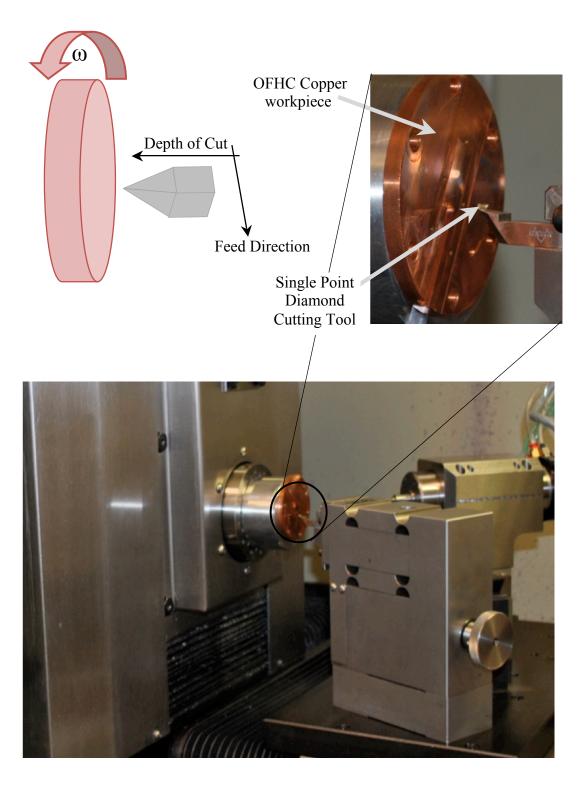

| FIGURE 4.7: Schematic representation and picture of actual diamond turning operation                                            | 69  |

| FIGURE 4.8: Picture of the diamond turned copper chip mount surface and the microscopic image for surface roughness comparison. | 70  |

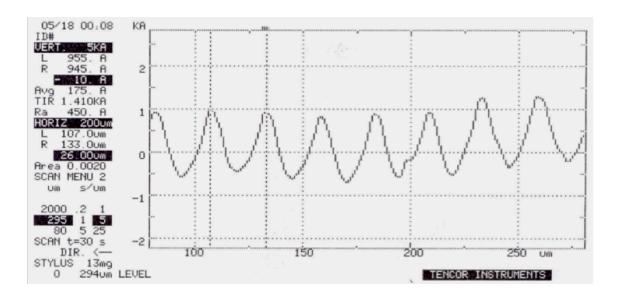

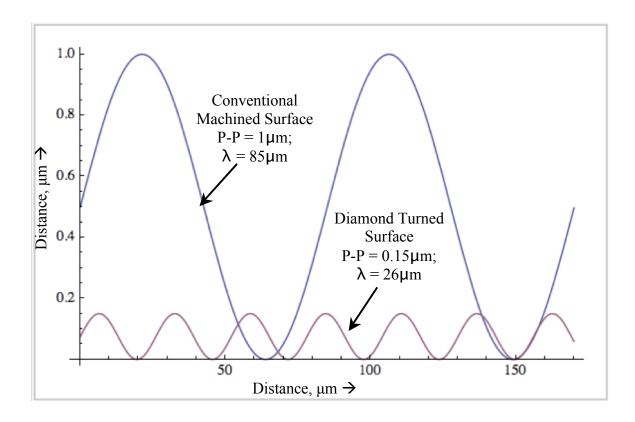

| FIGURE 4.9: Surface profile measurement and comparison of conventionally machined surface and diamond turned surface.           | 72  |

| FIGURE 4.10: Graphical representation of the conventional machined and diamond turned surface                                   | 74  |

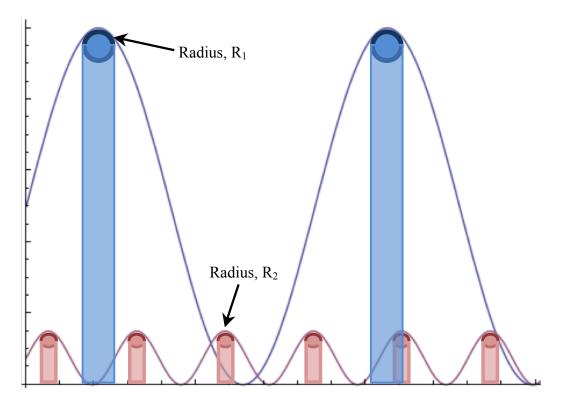

| FIGURE 4.11: Curve fit representation for approximating the contacting tip radius                                               | 75  |

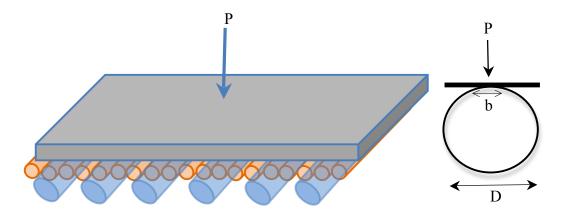

| FIGURE 4.12: Hertzian contact representation for cylinder and flat plate                                                        | 76  |

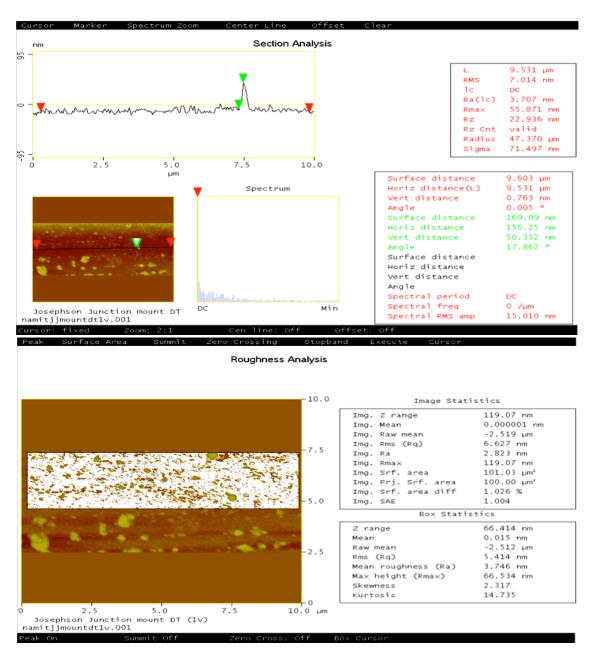

| FIGURE 4.13: Atomic force microscope (AFM) measurements for the diamond turned surface.                                         | 79  |

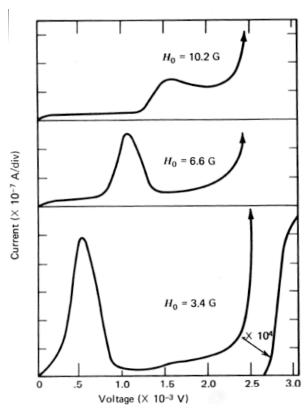

| FIGURE 5.1: Dependence of critical current in on incident magnetic field                                                        | 89  |

| FIGURE 5.2: MuMetal® magnetic shield enclosure for the JJA chip                                                                 | 92  |

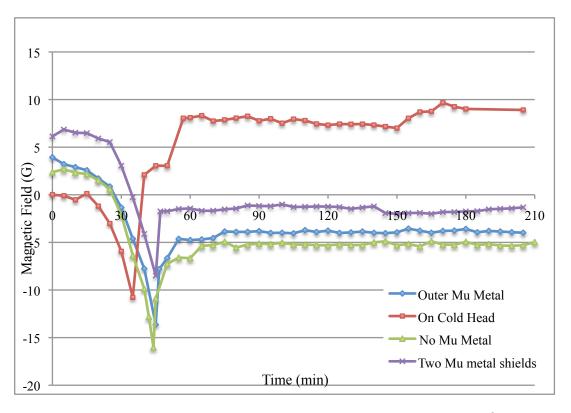

| FIGURE 5.3: Experimental results for different configurations of MuMetal® magnetic shields                                      | 94  |

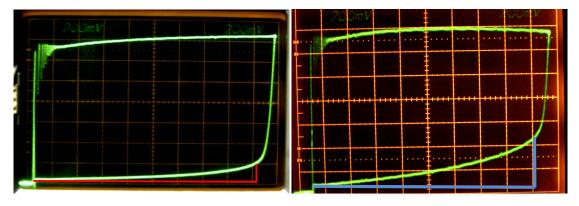

| FIGURE 6.1: I-V characteristic curve as an indicator of operating temperature of a JJA chip                                     | 98  |

| FIGURE 6.2: I-V curve of the 1-volt JJA chip displaying magnetic flux trapping                                                  | 100 |

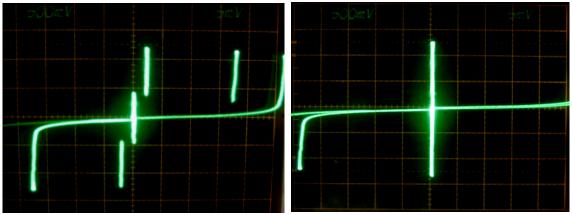

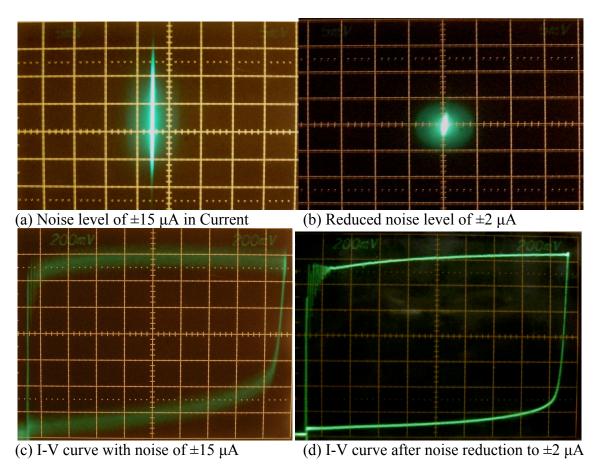

| FIGURE 6.3: Electromagnetic noise levels in the measurement system                                                              | 101 |

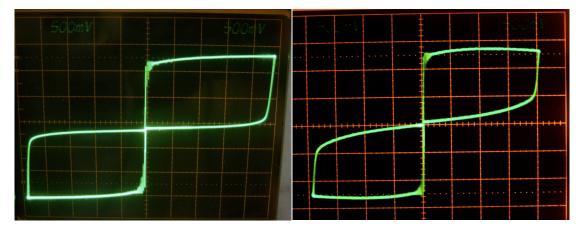

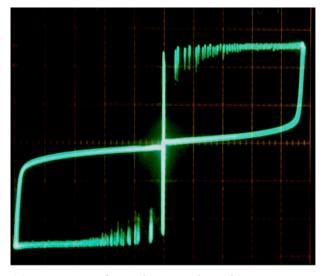

| FIGURE 6.4: I-V curves for the Josephson voltage standard system                                                                | 105 |

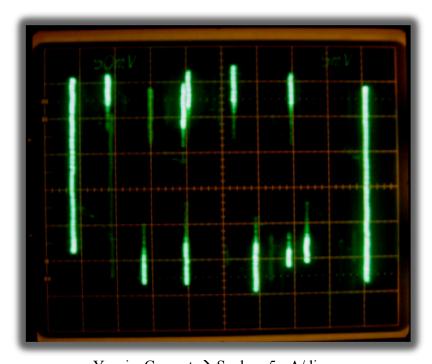

FIGURE 6.5: Voltage step representation for a 1-V JJA chip with an incident 76.5 GHz microwave power

108

# LIST OF TABLES

| TABLE 6.1: Frequency uncertainty and correction values                                             | 102 |

|----------------------------------------------------------------------------------------------------|-----|

| TABLE 6.2: Self test measurement results for $10 \ k\Omega$ test load                              | 103 |

| TABLE 6.3: Comparison of system parameters for the UNCC-JVS system and liquid helium Dewar system. | 106 |

## LIST OF ABBREVIATIONS

APSL Army primary standards laboratory

BCS Bardeen-Cooper-Schrieffer

CCR Closed-cycle refrigeration

DVM Digital voltmeter

EMI Electromagnetic interference

G-M Gifford McMahon

GPS Global positioning system

I-V Current-Voltage

JJ Josephson junction

JJA Josephson junction array

JVS Josephson voltage standard

NMI National Measurement Institutes

OFHC Oxygen free high conductivity

RF Radio frequency

RFI Radio frequency interference

SQUIDS Superconducting quantum interference devices

TMDE Test, measurement and diagnostic equipment

#### **CHAPTER 1: INTRODUCTION**

Today's US Army relies on increasingly sophisticated equipment and weaponry systems to provide the most accurate and efficient fighting force in the world. Unlike most of the weapons of the 20<sup>th</sup> Century, in today's world, most of the technologically advanced equipment and devices are electronically operated and controlled. The operational efficiency of these systems is directly dependent on the ability to accurately measure voltage for the purpose of calibrating the systems. This dissertation presents the work done in developing a portable voltage standard for use by the US Army Primary Standards Laboratory (APSL) to provide a field-ready standard for voltage against which in-service equipment could be calibrated. The voltage standard system presented here operates on the principle of the Josephson effect [1-4]. An integrated circuit chip consisting of an array of superconducting Josephson junctions produces a known constant voltage (10 volts or 1 volt, based on the chip), which is used as an intrinsic standard for voltage calibration. The focus of this work was to develop a fully operational prototype of the portable Josephson Voltage Standard (JVS) system and conduct a detailed investigation into determining and controlling all the factors affecting the stability of the system.

The portable JVS system relies on a Closed-Cycle refrigeration (CCR) system for cooling of the superconducting Josephson Junction Array (JJA) chip to the operating cryogenic temperature of 4.2 Kelvin. The stable operation of the JJA chip is highly dependent on the successful cooling of the chip and is very sensitive towards the presence

of any magnetic field or any electromagnetic noise in the measurement instrumentation. Design of the system presented here focuses on addressing these issues and successfully implements methods of eliminating or reducing these effects.

#### 1.1 Research Motivation

The International System of Units, SI units, was established to meet the need for a worldwide set of units that is uniform and coherent. The SI units are categorized into seven base units such as length, mass, time, electric current, temperature, amount of substance and luminous intensity. Out of the seven base units, ampere (electric current) is the only unit that is related to electrical measurements. The unit of 'Volt' is defined in terms of current, length, mass and time as "that electromotive force between two points on a conductor carrying a constant current of 1 ampere when the power dissipated between the two points is 1 watt." [5]

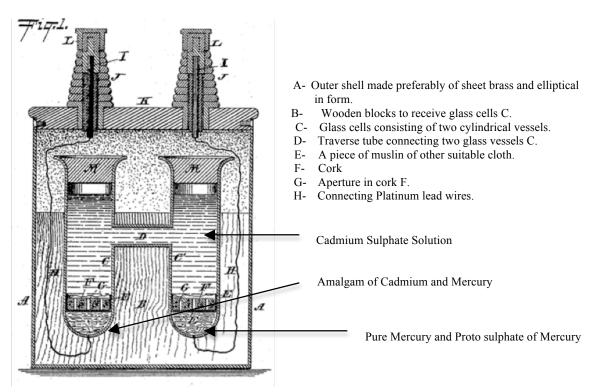

Prior to 1972, a Weston cell <sup>[6]</sup> formed the primary voltage standard and measurements were made using techniques which drew negligible current from the standard. A standard Weston cell delivers a constant electro-motive force of 1.019 volts at 20° C and is usually kept immersed in a temperature controlled oil bath protected from vibrations. Figure 1.1 shows the diagrammatic representation of the Weston voltaic cell from the patent issued to Edward Weston <sup>[6]</sup> in April 1893, where he mentions, "I have discovered a voltaic cell, the temperature coefficient of which is practically invariable; in other words, a cell which is free from temperature error, or in which the electromotive force does not depend upon the temperature of the cell. While a cell of this character may be applied to various uses, it will find its practical employment and be of the highest utility as a standard of measurement of electromotive force. There is, at the present time,

no absolute standard of the unit of electromotive force, (the volt) but there is a variety of cells termed 'standards' with which comparisons are made." He discovered that the electromotive force of all cadmium salts is practically independent of temperature change. As seen in Figure 1, the cell contains an amalgam of cadmium and mercury as the anode and a mixture of pure mercury and proto sulphate of mercury as the cathode; both the cells are then filled with a saturated solution of cadmium sulphate. Obviously, the operation of the Weston cell is highly dependent on the involvement of chemicals. If no appreciable current is drawn from the Weston cell, it will retain its voltage for years, but drift and transportability limit the uniformity of the voltage standard to about 1 ppm <sup>[7]</sup>. The uncertainty of measurements associated with the Weston cell directly translates to the uncertainty and the instability of the SI volt.

Figure 1.1: Diagrammatic representation of a Weston cell [6].

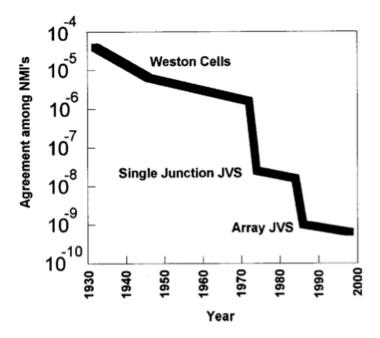

In order to achieve the SI volt, experiments were carried out that were difficult to conduct and produced results with unacceptable levels of uncertainty and nonrepeatability [8-10]. By the 1970's, many national laboratories started using the Josephson effect as the practical standard of voltage [11, 12] and currently most of the national labs around the world maintain their own JVS systems [13-17]. The stability of a Josephson volt depends solely on the stability of the frequency of an oscillating current across the Josephson junction. Today, metrologists have developed artifacts and experiments representing the SI volt that are stable and reproducible to a level approaching 0.001 parts in 10<sup>6</sup> (ppm) <sup>[7]</sup>. Details about the operational physics of the Josephson junction and the discussion on Josephson effect are covered in Chapter 2; only the developmental milestones of voltage standards are discussed in this introduction. The development and acceptance of voltage standards over the years have been at different levels in different parts of the world. National labs and measurement institutes around the world were using and relying on different measurement standards for voltage [8-11, 18-19]. Figure 2 is a semilog plot giving an overview of how the differences in dc voltage measurement among National Measurements Institutes (NMI's) have decreased [7].

Figure 1.2: Approximate level of agreement in dc voltage measurements among National Measurement Institutes (NMI's) from 1930-2000 [7]

The single junction Josephson voltage standard provided a much more stable voltage reference compared to the Weston cell but were very difficult to operate as they generated a very small voltage, on the order of 1 to 10 mV <sup>[7, 11-12]</sup>. Attempting to raise the output voltage by connecting two or more junctions in series aided in developing a series-array Josephson junction. The first practical 1 V Josephson standard was produced in 1985 <sup>[7]</sup>. Further advances in the superconductive integrated-circuit technology resulted in the production of 10V Josephson junction array chips. Standards such as the Josephson volt that depend on fundamental constants rather than physical artifacts are known as intrinsic standards. Although the Josephson voltage standard (JVS) does not realize the SI definition of the volt, it provides a very stable reference voltage that can be reproduced anywhere <sup>[7]</sup>.

The high accuracy metrology instrumentation involved with the voltage standard had been previously constrained to the laboratory environment because of various factors. The superconducting state of the Josephson array chip has historically been achieved by immersing the chip in liquid helium. Large volumes of liquid helium are stored in Dewars that are not suitable for mobile transfer. The low boiling point of helium (4.2 K) requires it to be stored under closed physical conditions. In order to maintain a constant level of helium in the Dewar, regular refilling is required. The constant replenishing of helium is a very expensive process and constrains the system to the locations that have abundant supply of liquid helium.

The United States Army Primary Standards Laboratory (APSL) recognizes the need for development of a transfer level calibration technology. The test, measurement and diagnostic equipment (TMDE) used by the US Army provides both fixed calibration operations situated on major Army posts and mobile calibration equipment used in the field on tactical calibration vehicles. The laboratory voltage standard incurs a lot of operational expenses because of the use of liquid helium, and in turn constrains the system to the non-transportable laboratory environment.

The United States Army TMDE and The University of North Carolina at Charlotte initiated a collaborative effort to develop a portable Josephson junction intrinsic voltage standard <sup>[20]</sup>. The goal of the project was to develop a prototype portable voltage reference standard system for installation in the Army's calibration van. The objective was to design a system that would operate independently of liquid helium and could be constructed by assembling off-the-shelf components, hence, simplifying component replacement.

# 1.2 Structure of Dissertation

The goal of this dissertation is to describe the development of the portable Josephson junction voltage standard system. The development of the operational prototype had many challenges associated with it. This dissertation is structured in such a way that it provides sufficient background for the reader to understand concepts related to the Josephson system and further details the factors affecting the development of and the proper operation of the Josephson voltage standard system.

The work contained in this dissertation is arranged in the following order: Chapter 1 provides an introduction to the field of voltage standards and further discusses the need for developing a prototype of the portable Josephson voltage standard system. This section provides an overview of the structure of the dissertation and topics covered in different sections. Chapter 2 provides an introduction to the voltage standards, briefly surveys the basic knowledge of superconductivity and physics behind the Josephson junction phenomenology and the basic structure of a portable Josephson voltage standard (JVS) system. The two most significant challenges with the design of the system are identified, namely, thermal management and magnetic field management. Chapter 3 further discusses the thermal management of the system, presenting an in depth analysis of the conduction cooling of the JJA chip and design of the CCR system. A mathematical model of the thermal system is developed and presented. In Chapter 4, a detailed analysis of the thermal contact conductance problem is addressed. The dependence of heat flow across the interfacing surface of the JJA chip and the cryo-cooler cold head was studied, and new mounting techniques were developed and tested. The operation and performance of a superconducting chip is highly dependent on the presence of any magnetic field in the vicinity, so Chapter 5 specifically addresses the challenges of magnetic shielding to reduce static magnetic fields and electromagnetic noise in the measurement system. After the complete assembly of the Josephson voltage system, the required tests were conducted to display the required operation of the system. The results for the various tests performed to prove the competency of the cryocooler based system are shared in Chapter 6 and are compared with the results obtained from other liquid helium based Josephson voltage standard systems operating in the laboratory environments. Chapter 7 presents the conclusions from the work.

#### CHAPTER 2: VOLTAGE STANDARD

The United States Army TMDE is responsible for calibration of the plethora of electronic equipment used by the Army. To assure the proper operation and accuracy of measurements, the equipment needs to be periodically tested and calibrated. The extensive use of these systems and equipments necessitates the calibration to be conducted outside the laboratory environment. A compact and transportable Josephson voltage standard needed to be developed for installation in the US Army calibration vans. At the heart of the Josephson Voltage Standard (JVS) system developed at UNC Charlotte is a Josephson junction array (JJA) chip that utilizes the superconducting characteristics of the material to generate a constant and stable voltage. This chapter provides some background for understanding operation of the system and discusses the design of the prototype JVS system.

### 2.1 Introduction

Superconductivity has been a subject of great interest for scientists, with numerous challenges in understanding the phenomenon and developing new applications. Even though the advances in the field of superconductivity have produced many applications utilizing superconducting magnets, magnetically levitated trains, superconducting quantum interference devices (SQUIDS), etc. the field still remains highly dependent on the technological advancements in the field of cryogenics. The low temperature superconductive devices operate at temperatures close to 4 Kelvin and these temperatures

are achieved with the help of cryogenic refrigeration systems. On another front, there have also been tremendous developments in the area of high-temperature superconductors with some materials with critical temperatures in the range of 130 K. The cooling of metals well below room temperature causes a significant reduction in the electrical resistance. Also, as the material approaches a temperature close to absolute zero, the energy of the material becomes very small and the flow of electrons in the conductor becomes negligible.

In 1911, Heike Kamerlingh Onnes <sup>[21]</sup> found out that steadily lowering the temperature of a mercury wire lowered the electrical resistance, and at 4.2 K, the resistance completely vanished. This characteristic state of no-resistance and pure conductivity achieved at a very low temperature was termed as the supraconductive state (now, commonly called superconductive state) and the materials displaying this extraordinary electrical property were called Supraconductors <sup>[21]</sup>. At extremely low temperatures, the overall energy of any material becomes very low; this change in the behavior causes the sudden drop in electrical resistance to diminishing values. At these temperatures the conduction of electricity in certain materials increase and hence the materials are known as superconductors. Onnes was awarded the Noble prize in physics in 1913 for his investigations on matter at low temperatures <sup>[222]</sup>.

## 2.2 Principles of Superconductivity

After the discovery of superconductivity by Onnes in 1911, the behavior of superconductivity was observed in many metals but there was a lack of clear understanding of the phenomenon and a satisfactory explanation at the microscopic level was not provided until late 1950's. In order for scientists to explore the nature of

superconductors or develop applications based on the behavior, it was necessary to understand the phenomenon in detail. In 1937, Fritz London, recognized that supraconductors are macroscopic quantum systems and are a result of manifestation of quantum phenomena on the scale of large objects [23-25]. In 1957, a satisfactory explanation of the superconducting behavior was given at the microscopic level by John Bardeen, Leon Cooper and Robert Schrieffer [26-27]. They were awarded a Nobel Prize in physics in 1972 for their in-depth explanation of the phenomenon of superconductivity based on the quantum mechanical behavior of electrons and the theory was named as the BCS theory of superconductivity.

# BCS Model of superconductivity:

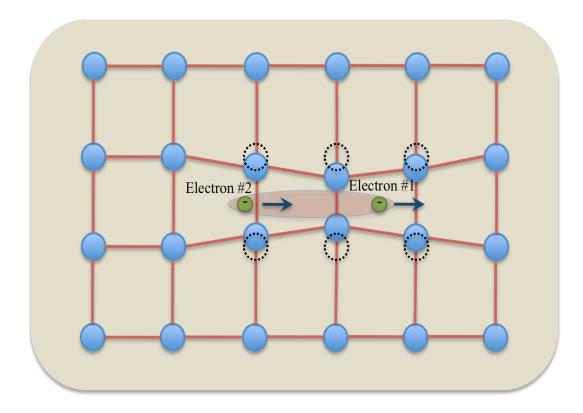

The behavior of electrons is vastly different in a superconducting state as compared to normal conductors. In a conductor, the electrical resistance causes loss of energy in the form of heat. As the electrons pass through the conductor they collide with impurities and imperfections in the crystal lattice and loose energy in the form of heat. Cooper [28] realized that atomic lattice vibrations were directly responsible for unifying the entire current. They forced the electrons to pair up and could pass all of the obstacles that caused resistance in the conductor. These pairs of electrons are known as Cooper pairs. Cooper and his colleagues knew that electrons which normally repel one another must feel an overwhelming attraction in superconductors. The answer to this problem was found to be in phonons, packets of sound waves, present in the lattice as it vibrates [29, 30].

According to the BCS theory, <sup>[26, 27]</sup> as one negatively charged electron passes by positively charged ions in the lattice of superconductor, the lattice distorts. This in turn causes phonons to be emitted, which forms a trough of positive charges around the

electrons. Before the electron passes by and before the lattice springs back to its normal position, a second electron is drawn into the trough. It is through this process that two electrons, which should repel one another, link up as a pair. The forces exerted by the phonons overcome the electron's natural repulsion. The electron pairs are coherent with one another as they pass through the conductor in unison. The electrons are screened by the phonons and are separated by some distance.

When one of the electrons that make up a Cooper pair passes close to an ion in the crystal lattice, the attraction between the negative electron and the positive ion cause a vibration to pass from ion to ion until the other electron of the pair absorbs the vibration. The net effect is that the electron has emitted a phonon and the other electron has absorbed the phonon. It is this exchange that keeps the Cooper pairs together. It is important to understand, however, that the pairs are constantly breaking and reforming. Because electrons are indistinguishable particles, it is easier to think of them as permanently paired. Figure 2.1 illustrates a wave of lattice distortion due to attraction to a moving electron pair. The figure also illustrates how two electrons forming a called Cooper pair become locked together. By forming a pair of two the electrons pass through the superconductor more smoothly.

Figure 2.1: Lattice distortion and electron Cooper pairs in superconductors.

The BCS theory provided a much deeper understanding in the phenomenon of superconducting behavior and was widely accepted as a valid explanation. When the atoms of the lattice oscillate as positive and negative regions, the electron pair is alternatively pulled together and pushed apart without a collision. The electron pairing is favorable because it has the effect of putting the material into a lower energy state. When electrons are linked together in pairs, they move through the superconductor in an orderly fashion. The average distance between the paired electrons is called the coherence length,  $\xi$ . The temperature, current density and magnetic field are the most important parameters to be considered for a superconductor. The Cooper pair can be broken by increasing the energy of the pair by thermal (critical temperature), kinetic (critical current density) or magnetic (critical field) interactions. As long as the superconductor is cooled to very low temperatures, the Cooper pairs stay intact due to the reduced molecular motion. As the

superconductor gains heat energy the vibrations in the lattice become more violent and break the pairs and as they break, superconductivity diminishes. The temperature, current density and magnetic field forms a *phase space*, in which the particular material exhibits superconducting characteristics.

#### Meissner Effect:

In 1933, Walther Meissner and R. Ochsenfeld [31] discovered a very interesting property displayed by superconductors. According to their findings, when a material is in the superconducting state, it does not allow a magnetic field to penetrate the superconductor. The magnetic lines incident on the superconductor cause a generation of electric current on the surface, which in turn causes magnetic field generation inside the superconductor that balances the field. The Meissner effect is displayed only for small values of the magnetic fields; at higher values, the field penetrates into the material and causes the loss of superconductivity.

# Brian Josephson:

In 1962, Brian Josephson, then a graduate student at the Royal Society Mond Laboratories, Cambridge, England, made an intriguing discovery in the field of superconductive tunneling <sup>[1]</sup>. After listening to a series of lectures from Professor Phil Anderson, a pioneer in the subject of tunneling supercurrents, Josephson was fascinated by the idea of "broken symmetry" in superconductors <sup>[2, 32, 33]</sup>. He then theoretically predicted and published his theory proposing an approach to the calculation of tunneling supercurrents between two metals when both metals are superconducting <sup>[1, 3, 4]</sup>.

The subatomic elementary particles like electrons display the quantum mechanical properties of both wave and particle. According to the theories, the waves can penetrate a

thin barrier which, based on the classical particle theory, would not be possible for an electron. If a thin layer of insulator separates two metals, the insulator should act as a barrier for the moving charge carriers in the metals. But, Josephson observed that instead of blocking the flow of electrons, occasionally there is a certain fraction of electrons that would mischievously penetrate through the forbidden region. This tunneling of the electrons through the forbidden region arises from the wave nature of the electron and causes a flow of weak current known as the tunneling supercurrents [3, 4, 33]. Brian Josephson's discovery in the field of quantum interferometry theoretically explained the influence of applied electric and magnetic fields to influence and control the flow of tunneling supercurrents. Later, the theory proposed by Josephson was experimentally confirmed by different groups [2, 33]. This phenomenon of tunneling supercurrents through a junction of two superconductors separated by a thin insulating barrier is known as the Josephson effect. The discovery of Josephson effect revolutionized many aspects of electronics and Josephson was rewarded with the Nobel Prize in Physics in 1973 for his pioneering research discoveries of tunneling phenomenon in solids.

## Physics of Josephson effect:

The electrons tunneling from one superconducting region to the other through an insulating barrier can penetrate the barrier without any voltage drop. This junction of weak electrical contact between two pieces of superconducting metal displaying the Josephson effect is commonly termed as a Josephson junction (JJ).

As materials are cooled down to a very low temperature, approaching absolute zero, some of them undergo a transition of material properties and start behaving as superconductors. If the material is cooled below its transition temperature,  $(T_c)$ , the

electrical resistance of the material drops to a very low value. The density of current that flows through the junction is characteristic of the geometry and material of the junction<sup>[7]</sup>.

When two superconductors are physically separated from each other, the electrons in each of them behave independently. The superconducting phase of the material is a position dependent parameter. Now, if the two superconductors are brought to within about 30 Å, single electron tunneling causes an exchange of quasiparticles [34]. Further, if the distance of separation is reduced to 10 Å, there is also a flow of Cooper pairs from one superconductor to the other causing the Josephson tunneling. In this situation the whole system of the two superconductors separated by the thin (~10 Å) dielectric barrier behaves to some extent as a single superconductor [26, 27, 34]. The electron pairs in the junction, tunnel through the barrier and cause a current flow. If the current flowing through the junction is lower than the critical current  $(I_c)$  there is no resistance against the flow and the voltage drop across the junction stays zero. If there is a magnetic field present in the region, it lowers the critical current of the Josephson junction. The lowering of the critical current doesn't affect the actual current flowing through the junction but the junction then develops a resistance to the flow because the actual current is now more that the critical current of the junction.

# 2.3 Josephson Junction Voltage Standard

Modern instrumentation requires very precise voltage measurements with high repeatability. Adopting the Josephson voltage standard (JVS) as the intrinsic standard for voltage fulfilled the need for such an accurate and stable measuring standard. The voltage standard currently adopted in the industry reproduces a unit volt by a quantum standard based on the Josephson effect [7-12]. Fundamentally, the Josephson effect is due to

tunneling of Cooper pairs formed by bound pairs of electrons occupying states with equal and opposite momentum and spin. The passing of a flux quanta through the Josephson junction of two weakly coupled superconductors produces a voltage across the junction. The flux quanta can be represented by

$$\phi = \frac{h}{2e} \tag{2.1}$$

where, h denotes Planck's constant and e is the elementary charge. Note that 2e represents the charge of the electron pair. Among the many predictions that Josephson made associated with the tunneling of electrons, the most significant was the relation between the application of an oscillating current across the junction and the generation of a DC voltage. He stated that when a DC voltage, V, is applied across two superconductors separated by a thin insulating barrier, an oscillatory current, of frequency f, is generated across the junction, as shown in Equation 2.2  $^{[3,4]}$ .

$$f = \frac{V}{\phi} \tag{2.2}$$

Using state of the art time references, such as the cesium atomic clocks, the measurement of frequency can be precisely and accurately controlled. The Josephson effect thus reduces the production of voltages to the determination of a frequency. If the junction is operated at a non-zero voltage, V, it acts as an oscillator of a known frequency, thus a Josephson junction is an ideal voltage controlled oscillator. The voltage-to-frequency conversion constant, also known as the Josephson constant,  $K_J$ , has a value of  $^{[7]}$

$$K_J = 483,597.9 \frac{GHz}{V} \tag{2.3}$$

The very high frequency and low voltage of this oscillation made it very difficult to

observe and measure. However, when an ac current at frequency f is applied to the junction, the junction oscillation tends to phase-lock to the applied frequency.

If during the phase-lock, the Josephson junction is irradiated with a microwave frequency f, the flow of flux quanta (known as the ac Josephson effect) produces constant voltage steps at a voltage  $V_n^{\{7,35\}}$ .

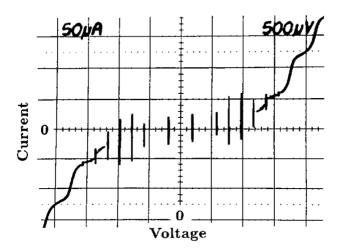

$$V_n = n \frac{h}{2e} f \tag{2.4}$$

Usually the junction also phase-locks to the harmonics of f, resulting in a series of steps represented by n ( $n = 1, 2, 3, \ldots$  denotes the integer step number representing the number of flux quanta which are transferred by each period of the microwave). These steps are a characteristic of the Josephson junction and can be seen on the Current-Voltage (I-V) curve. Figure 2.2 is the representation of the I-V characteristic of a typical Josephson junction with microwave power applied to it.

Figure 2.2: I-V Characteristic of a single Josephson Junction with 96 GHz microwave power applied [7].

The effects of microwave on the Josephson junction were experimented with by several groups and a detailed understanding was developed [36-39]. In adopting the ac Josephson effect as a practical standard of voltage, it was necessary to specify the exact value of the Josephson constant,  $K_I = \frac{2e}{h}$ , as that was the constant used in translating the value of frequency to voltage. Initially, many national laboratories used the ac Josephson effect to measure the more accurate value of 2e/h [11, 12, 18, 19]. By the early 1970's, most of the laboratories started using the ac Josephson effect as the practical standard of voltage [7]. Effective January 1, 1990, the new international definition of the practical unit of voltage was accepted and adopted by all standards laboratories and is given by [18]

$$V = \frac{nf}{K_{I-90}} \tag{2.5}$$

with,  $K_{J-90} = 483\ 597.9\ \frac{GHz}{V}$ . The uncertainty of  $K_{J-90}$  is 0.4 ppm.

The discovery of a single Josephson junction and its capability to produce a highly stable voltage was a major breakthrough in the field of voltage standards. One of the biggest problems with the single junction voltage standard was that in the conventional operating mode the amplitude of the output voltage was in the order of millivolts. The thermal voltages induced by the temperature difference and other noise sources induced a major source of uncertainty in the measurement of standard cell voltages. The Josephson voltage standard was improved by connecting several junctions in series to produce larger quantized voltages. A single Josephson junction typically produces a quantized voltage from 1 mV up to 5 mV when driven with microwaves near 10 GHz <sup>[7]</sup>. Creating an array of Josephson junctions in series generated higher voltages, but these experiments had their own problems associated with stability, microwave distribution among junctions,

etc. A joint effort between the National Bureau of Standards (NBS) in the USA and the Physikalisch-Technische Bundes-Anstalt (PTBA) in Germany resolved these problems and created the first large Josephson junction array in 1984 <sup>[7]</sup>.

To achieve measurable quantities of voltage using the Josephson junctions, highly integrated series arrays are used to achieve output voltages of 1 V or 10 V. These Josephson Junction Array (JJA) voltage standards can consist of up to about 20,000 Josephson junctions for a 10 V JJA chip. In order to obtain the largest voltage value from the smallest number of junctions, the junction array is designed in such a way that it delivers uniform microwave power to most of the junctions. Figure 2.3 is a diagrammatic representation of the JJ arrays fabricated on a silicon wafer using highly advanced microfabrication techniques. The series of superconducting junctions on the Josephson chip consists of microwave striplines that can propagate microwave power with relatively low loss.

Figure 2.3: Diagrammatic representation of Josephson Junction Array and the circuit. [7]

Several national and military standard laboratories around the world are now using the Josephson junction array (JJA) voltage standard system because it provides very high accuracy and least uncertainty in calibration <sup>[13-17]</sup>. However, for the JJA chip to achieve the required operating temperature, majority of the laboratory designs incorporate large

volumes of liquid helium. Use of liquid helium Dewar to cool the JJA chip restrains the voltage standard system to the laboratory environment, typically requires significant manual interaction and increases the operating cost of the system. This research focuses on developing a portable Josephson voltage standard system that operates without the use of liquid helium to cool the chip, has the same or better operating accuracy as that of a laboratory installed liquid helium based system, provides a more consistent cool-down cycle to prevent trapping of magnetic flux, and offers the mobility that allows equipment to be transported to the field.

# 2.4 Dewar-based Voltage Standard system

A schematic of a typical liquid helium Dewar based Josephson voltage standard system is shown in Figure 2.4. As shown in the figure, the primary components are: Cryoprobe to hold the Josephson junction array (JJA) chip, JVS controller 1002, Phase Matrix 578 microwave counter for frequency phase locking, oscilloscope, computer and the scanner along with check standards and other device under test (DUT).

Figure 2.4: Liquid helium Dewar based Josephson voltage standard system.

From the operational point of view, the components can be categorized as a) the thermal system, b) magnetic shielding and electromagnetic noise suppression, c) microwave source, and d) measurement equipment. In designing an active system, the thermal system is of principal interest; however, significant modifications are also required for the shielding components since the cryocooler is an electromagnetic device and induces noise. These modifications are discussed in the following sections.

# 2.5 Design of a Portable System

Like the Dewar-based system, a cryocooler based portable JVS system consists of

most of the same components; however, significant development is required in the areas of thermal management and electromagnetic noise suppression. In the Dewar system, the chip is submerged in liquid helium, which provides three-dimensional cooling. Once the JJA chip is submerged in liquid helium it maintains a uniform temperature of 4.2 K, till there is sufficient liquid helium present in the Dewar. Once the level of liquid helium starts to drop, the superconducting junctions start to heat up and this can be seen in the operational performance of the JJA chip. In case of the CCR based JVS system, the JJA chip is mounted on a chip mount, which is attached to the second stage of the cryocooler, operating at 4.2 K. During regular operation of the cryocooler, the chip mount reaches a temperature of 4.2 K and the JJA chip is cooled by conductive heat transfer. The surroundings of a JJA chip are maintained under a state of vacuum, because of which there is no thermal convection. Under this situation, cooling of the JJA chip is through surface contact between the JJA chip and the chip mount. The thermal, magnetic, microwave and measurements systems are briefly discussed in this section, and at the end an overview of the complete assembled system is provided.

# 2.5.1 Thermal and Cryogenic System

The Josephson junctions are made of superconducting materials (niobium, in our case) that display their characteristic superconducting properties only when cooled below their critical temperature of 9.2 K. So, one of the most critical components while constructing a voltage standard system operating on the principle of Josephson effect is the cryogenic system. The cryogenic system is solely responsible for achieving the operating temperature of 4.2 K for the stable operation of the Josephson junction array (JJA) chip. At the heart of the cryogenic system is a closed circuit refrigeration unit

consisting of a Sumitomo cryocooler cold head (RDK-415D) [45, 46] and a Sumitomo compressor unit (CSA-71A) [47]. The cryocooler system cold head is a two-stage Gifford-McMahon (GM) cycle cryo-refrigerator. The function of the cold head is to produce continuous refrigeration at temperatures in the range of 25 K - 40 K at the first-stage cold station and in the range of 3.5 K - 4.2 K for the second stage cold station, based on the heat load of the system [45-47]. The cryocooler is enclosed in a cylindrical vacuum chamber constructed of aluminum. An Alcatel mechanical roughing vacuum pump is connected to the chamber with a capability of achieving a vacuum of 1x10<sup>-3</sup> Torr. The JJA chip is secured on a precisely designed and machined Oxygen Free High Conductivity (OFHC) copper chip mount and the chip mount is mounted on the 4 K cold head of the cryocooler. The instrumentation of the system is connected to the JJA chip using a set of six wires (AWG-32). The six wires are soldered to a FR-4 fingerboard that establishes contact with the pads on the JJA chip and are used for biasing the chip and measuring the voltages. All the wires are thermally anchored at the 4 K stage and the 50 K stage to reduce thermal load. The detailed design of the chip mount and the JJA chip holder is discussed in Chapter 3. Inside the vacuum chamber a thermal radiation shield is used to eliminate the radiation heating of the JJA chip and other crucial components. The CCR system for cryocooling delivers the compressed helium gas to the cryocooler unit and achieves the temperature essentially same as that of a liquid helium based system, without the involvement of handling liquid helium. An in-depth discussion is provided on the complete assembly and design of the cryocooling system in Chapter 3.

## 2.5.2 Magnetic Shielding

The operational performance of a Josephson junction is dependent upon the presence of any external magnetic fields. The presence of magnetic fields higher than a critical value for the particular superconducting material prevents the material from achieving the superconducting state. As the temperature of the Josephson junction is lowered below the critical temperature, any magnetic field present in the vicinity of the junction can cause magnetic 'flux trapping'. As the junction transitions into the superconducting state, due to the Meissner effect, eddy current loops start forming within the junctions and can cause trapping of magnetic flux. Any magnetic field greater than the critical field of the superconductor prevents the circuit from entering the state of superconductivity.

The best way to avoid magnetic flux trapping is to create a magnetically shielded region around the JJA chip and to cool the chip at a slow and constant rate. The voltage step transitions are very sensitive to any induced noise; hence, all the wires go through an RF-filter box and all the other electronic components are grounded. The complete details about the design of magnetic shields and RF filters along with the results for the performance are presented in detail in Chapter 5.

## 2.5.3 Microwave Source

The characteristic equation for a Josephson junction, f = 2eV/h, represents the frequency at which the current oscillates when a dc voltage, V, is applied across the junction. The oscillating current in the junction has a very high frequency and low magnitude. Because of the nature of this current, it is very difficult to measure it directly, hence, an ac voltage of a known frequency f is applied to the junction and the oscillation phase-locks to the applied frequency and provides a very stable reference voltage.

The microwave energy required to operate the Josephson junction chip is generated by a Gunn diode oscillator operating in the range of 77 GHz + 2 GHz. Since, the performance of a Josephson voltage standard is dependent on the stability of the frequency source, a very low-noise and stable operation of the millimeter-wave source is necessary. The system is designed to phase lock the millimeter-wave Gunn diode oscillator synchronized to an external reference source operating at 10 MHz. An EIP Model 578B Source Locking Microwave Frequency Counter [48] is used to perform the frequency measurement as well as phase lock the external signal source. The EIP-578B has the capability of either using an external frequency source or the internal time base crystal oscillator can be selected to maintain a long-term accuracy and stability. The external reference source used for the system is a Datum Inc. manufactured ExacTime ET 6000-75 GPS Time Code and Frequency Generator [49]. The ET-6000 contains a voltage controlled Crystal oscillator; the Global Positioning System (GPS) Timing Unit includes the GPS Main module, an antenna and a coaxial cable for interconnections. The GPS Timing Unit determines time and frequency by measuring the time of arrival of the precise timing mark and monitoring time and frequency data from the Navstar satellite constellation [49]. The GPS Unit provides a corrected 1 pps output signal and a 10 MHz Sine wave [49]. The 10 MHz signal output from the GPS unit is provided to the EIP-578B locking counter as the external reference by connecting a coaxial cable from the back of the GPS unit (connector J6) to the back of the EIP (connector J5, 10 MHz Timebase-Ext).

The external frequency reference is utilized to obtain an accurate and stable output from the Gunn diode oscillator. The Gunn assembly consists of the Gunn diode, an isolator, a coupler, a mixer and an attenuator. Figure 2.5 shows a picture of the Gunn

assembly. The Gunn diode is connected to the Gunn Oscillator Power Supply (GS1002)<sup>[50]</sup> by a coaxial cable and controls the output frequency of the Gunn diode by adjusting the supplied voltage from the GS1002. The isolator attached right next to the Gunn diode prevents any feedback to the Gunn diode. The coupler and the mixer are an essential part of the lock-in subsystem; the output from the mixer is fed to a frequency counter (EIP 578B), which determines the frequency of the signal, and the difference in frequency is used to send a signal to the Gunn Oscillator Power Supply (GS1002) controller that adjusts the bias voltage sent to the Gunn diode to vary its output frequency. This iterative process compares the frequencies between the reference and the local oscillator to stabilize the local oscillator to the reference. An attenuator adjusts the power output of the system and the output from this system is delivered to the JJA chip through an assembly of waveguides.

Figure 2.5: Gunn Diode assembly

## 2.5.4 Layout of the Portable System

In the previous section, different subsystems of the Josephson Voltage Standard system were introduced and briefly discussed. This section presents an overview of the complete design layout of the portable JVS system. Figure 2.6 gives a diagrammatic representation of the complete assembly along with the connection and wiring diagrams. All the components of the system are housed in a standard rack of approximate dimensions 56 cm x 82 cm x 195 cm. The bottom half of the rack contains the refrigeration unit for the cryocooling system including the compressor, radiator and cooling fan along with other electronic components for the operation of the cryocooler. The top half contains the vacuum chamber that encloses the two stages of cryocooler (cold end) and the assembly holding the Josephson Junction Array (JJA) chip. The pump for circulating compressed helium through the cryocooler is attached at the top end of the vacuum chamber and is connected to the compressor unit with flex-line for transporting helium. The cryocooler pump circulates the compressed helium gas through the cryocooler tubes to cool the cold head and the JJA chip. The chamber is connected to the vacuum pump that creates a vacuum of close to 1 mTorr during the operation of the system.

All the instrumentation components of the system are stacked in the top portion of the rack with their front panel completely accessible to the operator. The connection of these components can be seen in Figure 2.6. A GPS antenna installed at the roof of the building acquires accurate data of time and frequency and transmits it to the GPS receiver (ET-6000-75). Using the external reference obtained from the GPS system, the millimeter wave subsystem (consisting of EIP 578B, the Gunn diode assembly and the GS 1002)

generates highly accurate and stable microwaves that are transmitted to the JJA chip by an assembly of standard WR-12 waveguides for the excitation of the superconducting junctions.

Figure 2.6: Diagrammatic representation of the assembled portable Josephson Voltage Standard System.

Another key component of the instrumentation assembly is the JVS1002 <sup>[51, 52]</sup> controller. Since the primary purpose of voltage standard system is to measure the terminal voltage at the JJA chip, the JVS system controller controls and automates the complete system. The JVS1002 is the main controller for the JVS system and is

connected to the system computer via the IEEE-488 port. The JVS1002 controller can be operated and controlled manually or by the NISTVolt <sup>[53]</sup> (trademark NIST) software installed in the system computer. Along with making crucial measurements required for the operation and conducting calibrations with the Josephson Voltage Standard system, the JVS1002 controller provides the bias current for the JJA chip and monitors the voltage at the JJA chip. The connecting wires from the JVS1002 controller to the JJA chip pass through RFI filters that eliminate any noise signals generated due to external factors.

A high performance digital nanovolt meter, HP 34420A, is connected to the JVS controller with an IEEE-488 interface. A set of cables providing the measurement of output voltage from the JJA chip exit the switching panel of the JVS1002 and provide the signal input for the digital voltmeter (DVM). Interface of the voltmeter with the NISTVolt software on the system computer provides the capability of controlling the DVM and obtaining the measurement data during the regular operation of the system as well as during the calibration process involving other equipment and/or other Josephson systems.

The rest of this dissertation is dedicated to discussing and presenting the in-depth research carried out during the development of each subsystem and presenting the results obtained from the UNC-Charlotte Josephson Junction Voltage Standard System.

### CHAPTER 3: THERMAL MANAGEMENT

The Josephson junction array based voltage standard system is a widely accepted do voltage standard because of its stability and high accuracy of measurement. The generation of voltage, 1 V or 10 V, and the operation of the system are dependent on the temperature achieved by the JJA chip. The Josephson voltage standard systems currently used typically utilize liquid helium as the cryogen for cooling the JJA chip. The chip is securely mounted on a cryoprobe and the complete assembly is immersed in a liquid helium bath. The superconductor utilized for fabrication of the Josephson junctions are operated at a temperature close to the liquid helium temperature of 4.2 K. The use of liquid cryogen makes it logistically difficult to provide a transfer level voltage standard calibration system; so a portable JVS system is designed using closed cycle refrigeration system and the details of the design are discussed in this chapter.

# 3.1 Cryocooling System

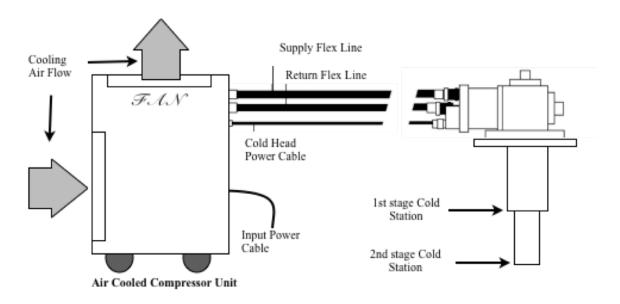

Commercially, there are different closed circuit refrigeration (CCR) systems available that can be built to customized specifications. The University of North Carolina at Charlotte Josephson Voltage Standard (UNCC-JVS) system utilizes a high efficiency closed cycle cryogenic refrigeration system to achieve an operating temperature in the vicinity of 4 K at the JJA chip surface. The complete cryocooler system was manufactured by Sumitomo Heavy Industries and consists of a Cold Head (RDK-415D), compressor unit (CSA-71A), helium flex lines and Cold Head power cables [45-47]. Figure

3.1 (a), provides a diagrammatic representation of the complete cryocooling system consisting of the air cooled compressor unit, the cold head, the helium flex lines and the power cables operating the cold head and Figure 3.1(b) shows the cross section of the second stage cold head displacer.

(a): Sumitomo Cryocooling system [45-47].

(b): Cross section of the Cryocooler Second stage regenerator [45-47].

Figure 3.1: Cryocooling System

The RDK-415D 4 K Cold Head is a two-stage Gifford-McMahon (GM) cycle cryorefrigerator that produces a continuous closed-cycle refrigeration. Depending on the heat load imposed on the system, the cold head achieves temperatures of 25 K to 40 K at the first-stage cold station and 3.5 K to 4.2 K at the second-stage cold station [45-47]. As shown in Figure 3.1, the assembly of the cold head consists of three major components, namely the drive unit, the cylinder and the displacer generator assembly, which is located inside the cylinder. The second stage displacer consists of lead (Pb) spheres, which enable the 2<sup>nd</sup> stage to achieve temperature of around 10 K <sup>[45]</sup>. Further, magnetic rare earth regenerator material HoCu<sub>2</sub> (Holmium-Copper<sub>2</sub>) is used in the 2<sup>nd</sup> stage displacer to achieve an operating temperature of 4 K  $^{[54,\ 55]}$ . Another regenerator material,  $Gd_2O_2S$ (Gadolinium Oxide Sulfide, GOS) is also used; because of its high volumetric specific heat a lower temperature is achieved at the cold head and allows significantly better cooling capacity to achieve an operating temperature of 4 K [45]. The use of rare earth regenerator material enables the Cold Head to have a second stage refrigeration capacity of 1.5 W at 4.2 K.

The cold head of the cryocooler is connected to the compressor unit with helium gas supply connectors. The compressor unit controls the high-pressure flow of helium gas to the cold head cylinder. During the operation cycle, the high-pressure (1.65 MPa at 20° C) helium gas passes into the displacer-regenerator assembly, comes out through the displacer-regenerator assembly to the crank case through the motor housing and finally returns to the compressor unit through the helium gas return connector [45]. The helium gas expansion in the displacer-regenerator assembly provides the cooling condition for first and second-stage cold stations. For further details on the operation of the cryocooler,

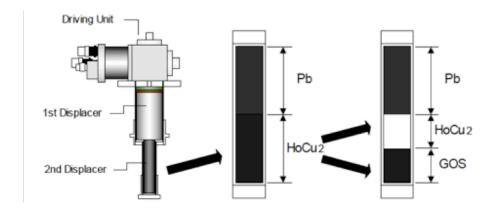

the reader should refer to references on the Gifford-McMahon (GM) refrigeration cycle and/or the Sumitomo Cryocooler operation manual <sup>[45-47]</sup>. The Sumitomo system required either 20 meter flex lines or 6 meter lines combined with buffer tanks. In our case, the 6 m flex lines were used with buffer tanks to facilitate packaging the unit in the instrumentation cabinet; the supply and return buffer tanks are inserted between the compressor unit and the flex lines. Figure 3.2 shows a diagrammatic representation of the complete system assembly.

## 3.2 Vacuum System

The complete cryocooling system consists of commercially available components that can be repaired or replaced as needed. For achieving the temperature of 4 K at the cold head of the cryocooler the two-stages of the cryocooler must be enclosed in a vacuum chamber. The vacuum chamber is created by machining an aluminum cylinder to surround the two stages of the cryocooler and is attached to the base of the motor of the cryocooler, as shown in Figure 3.2. An Alcatel mechanical vacuum pump is used to draw down the vacuum. A fixture is created across the vacuum chamber so that the chamber and the cryocooler can stand independently. For the operation of the cryocooler, first a high vacuum of near 1 x 10<sup>-3</sup> Torr is achieved in the chamber. The high vacuum environment surrounding the first and second stages of the cryocooler helps to ensure a low heat load at the cold head by nearly eliminating losses due to convection, thereby improving cryocooler efficiency. The vacuum inside the chamber is monitored by a pressure sensor connected to the vacuum line and is displayed on a pressure gage for convenience of the operator. Once the chamber reaches a vacuum of 10 mT, the cryocooler is turned on to begin the cool down cycle. The cooling of the cold head helps draw the vacuum down further by cryo-pumping. Silicon diode temperature sensors attached to the 1<sup>st</sup> and 2<sup>nd</sup> stage of the cryocooler monitor temperature at the cold head during cool down, which takes approximately 120 to 150 min. Figure 3.2, provides a diagrammatic representation of the assembled cryogenic and vacuum system.

Figure 3.2: Diagrammatic representation of the cryocooling and vacuum system.

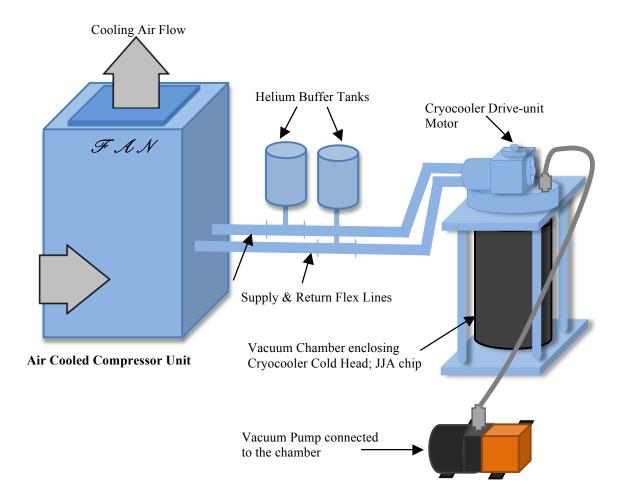

The complete voltage standard system needs to be built in such a way that it can be rack mounted in the standard cabinet of size 56 x 82 x 195 cm. The components of the closed circuit cryocooling system and the vacuum system require careful packaging to fit into the cabinet. The compressor unit (CSA-71A) made by Sumitomo Ltd. has physical

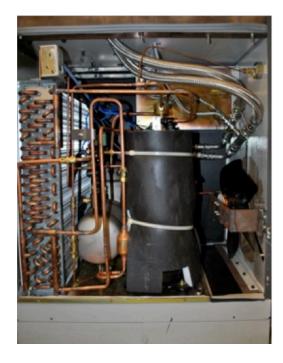

dimensions larger than the standard rack. So, in order to make sure that all the components of the system fit properly in the rack, the compressor unit was disassembled and the internal components, like the helium gas storage tank, filter, compressor capsule, adsorber, radiator, cooling fan, switches, electronic control box, etc., were restructured and fitted to a newly designed enclosure for the compressor unit. The airflow of the compressor unit was rearranged to provide optimal cooling within the cabinet. The flow of gas and oil in the compressor unit was taken into consideration to ascertain proper and safe operation of the unit. The original design of the CSA-71A unit had the air intake on the front face of the unit and the air discharge including the fan located on the top face of the unit. In the new design of the compressor unit, the air inlet is positioned in the front of the unit and the air discharge unit, including the fan, is moved to the back of the compressor unit. Figure 3.3 shows the assembled compressor unit and the vacuum system mounted on the standard rack. The bottom portion of the rack is physically separated from the top of the rack using an aluminum plate that also acts as a base for mounting the vacuum chamber. The vacuum pump, helium buffer tanks and the fixture holding the cryocooler and the vacuum chamber are positioned on top of the aluminum plate. The six-meter long helium flex supply and return lines are securely fastened to the sides of the rack. These lines, coupled with the buffer tanks, allow limited compliance in the system for dynamics, preventing the option of replacing the flex lines with hard fittings. The vacuum chamber and the cryocooler are mounted on the separating aluminum plate and sit on top of a spring-damper suspension system. The suspension system provides shockabsorbing capabilities to the vacuum chamber, which holds the highly sensitive JJA chip.

Figure 3.3: Redesigned compressor unit, cryocooler assembly and the vacuum system mounted on a standard rack mount.

## 3.3 Mounting of Josephson Junction Array chip

The complete assembled cryocooling system has the capability to cool the second-stage cold station of the cryocooler in the range of 3.5 K to 4.2 K, depending on the heat load of the system. For the Josephson Junction Array (JJA) chip to operate and provide the specified performance, it needs to be cooled down to a temperature below the critical temperature of niobium (9.2 K). Once the system was assembled, it was tested using the procedures discussed earlier and a temperature of 3.5 K was experimentally achieved and measured on the cold head of the cryocooler using silicon diode temperature sensors.

A fixture that would allow the chip to establish an efficient thermal conduction path to the cold head was required in order to cool the JJA chip to the operating temperature. The fixture was also necessary to securely hold the chip and restrict motion of the chip in any direction. Figure 3.4 shows images of the JJA chip mounting fixture (fabricated out of Oxygen Free High Conductivity (OFHC) copper) and other critical components. The JJA chip sits on the middle pedestal of the chip-mount and a piece of FR-4 surrounds the chip, as seen in Figure 3.4 (a). The pedestal of the JJA chip is machined to such a thickness that the FR-4 surround creates a raised wall surrounding the chip, hence completely restricting any lateral motion of the chip. The electrical connections for providing the bias current and measurement of the voltage are established using copperberyllium (Cu-Be) fingers fabricated on the FR-4 fingerboard, as shown in Figure 3.4 (d) and (e). The FR-4 fingerboard must be maintained at a controlled height to ensure sufficient but limited force on the chip to prevent damage. Also, it is required to have the microwave power delivered to the Josephson junctions on the chip. The fixture is designed in such a way that the opening on the microwave waveguide delivers the microwaves to the fin-line antenna fabricated on the JJA chip, which is essential for the actuation of junctions on the chip. The positioning of the chip with respect to the waveguide opening can be seen in Figure 3.4 (b).

Figure 3.4: (a) Image of chip mount with the JJA chip and the FR4 surround; (b) position of waveguide and JJA chip; (c) dimensional representation of chip mount; (d) FR4 circuit board with Cu-Be spring finger contacts, and (e) complete assembly on chip mount.

The OFHC copper chip mount sits on a set of six copper posts and is firmly anchored to the cold head of the cryocooler using brass bolts. The copper posts help in holding the magnetic shields that create an envelope of low magnetic flux region around the JJA

chip; the use of these magnetic shields will be explained during the discussion on the design of magnetic shields in Chapter 5. Figure 3.5 shows the complete assembly of the JJA chip mount attached to the cold head of the 4 K-second stage of the cryocooler. The magnetic shields are eliminated from this picture for clarity. The chip mount has a silicon

Figure 3.5: Image of the chip mount assembly attached to the 2<sup>nd</sup> stage cold head of the cryocooler.

diode temperature sensor attached to it for the measurement of surface temperature as well as a Hall sensor for measuring the magnetic fields in the vicinity of the JJA chip. During operation of the Josephson voltage standard, heat is produced from the incident microwaves and any thermal paths such as sensor wires that contact the outside of the

chamber. The 1 volt JJA chip consists of around 2000 superconducting junctions (20,000 for a 10 V chip) that need to be maintained below the critical temperature of the superconductor. As the junction reaches a temperature higher than, or close to, the critical temperature of niobium it looses the property of superconduction. Hence, the rate of cooling of the chip should be greater than the rate of heat produced during the operation. The 'heat-lift' of the system is calculated considering all the sources introducing heat [79]. As shown in Figure 3.4 and 3.5, the Cu-Be (Copper Beryllium) fingers on the circuit board establish a physical contact with the contact pads on the JJA chip and on the other side of the fingerboard the Cu-Be fingers are soldered to six copper wires (AWG-32). This set of six wires connect the JJA chip to the system controller and provide the bias current to the chip while measuring voltage across the circuit. One end of these copper wires is connected to the chip and the other end is soldered to the connector, which leads them outside the vacuum chamber. Having one end of the wire at the chip and the other end at room temperature provides a direct thermal conduction path from the chip to room temperature, approximately 295 K, and adds to the heat load at the JJA chip. To reduce the temperature gradient along the length of the wires, all the copper wires and the sensor cables are thermally anchored to the body of the cryocooler at the first stage, at 50 K, and at the second stage at 4 K.

#### 3.4 Thermal Radiation Shield